# Transformer Feedback based CMOS Amplifiers

Venumadhav Bhagavatula Department of Electrical Engineering University of Washington Seattle, Washington 98195-2500 Email: bvenu@uw.edu

*Abstract*—Analysis of several impedance matching networks used in both common source and common gate amplifiers with reactive feedback are presented. Five fundamental topologies for transformer feedback based closed-loop amplifiers are identified and their relative merits with respect to silicon area and power consumption are discussed. In addition, a design methodology to achieve both narrow and wideband matching is derived. A 5 GHz wideband amplifier designed in a TSMC 90-nm CMOS process is used to benchmark the different schemes. The calculated input impedance is compared with simulation results.

#### I. INTRODUCTION

Many modern RF and analog front ends need to support a high fractional bandwidth for multi-standard and high datarate applications. Traditionally, open loop amplifiers have been used in narrow-band front ends due to the low power gain associated with older CMOS transistors at RF. Past implementations of wideband amplifiers have been realized using either distributed or multi-order LC networks. In advanced CMOS technology nodes, the unity power gain frequency,  $F_{max}$ , is on the order of several hundred GHz. This allows the possibility of exploiting resistive or reactive feedback (f/b) to trade off the extra open-loop gain afforded by modern CMOS devices, for a wider-bandwidth and more tunable amplifiers. However, certain design considerations must be taken into account while selecting the feedback topology. For example, while resistive feedback can provide a small form-factor solution, the thermal noise added by the feedback resistor can be prohibitively large for applications requiring maximum sensitivity. In contrast, reactive feedback using inductors or transformers avoids the use of noise-inducing resistors, but at the expense of utilizing significantly more silicon area. Moreover, integrated transformers have gained acceptance because of their usefulness in circuits requiring differential-to-single ended conversion and by providing additional flexibility to couple in a DC-bias.

There are five basic topologies for transformer-based feedback amplifiers (TBFA):

- Source-Gate f/b-Common Source (SGFB-CS) [1], [2], [3]

- Source-Gate f/b-Common Gate (SGFB-CG) [4]

- Drain-Gate f/b (DGFB) [5], [6]

- Drain-Source f/b-Common Source (DSFB-CS) [7], [8]

- Drain-Source f/b-Common Gate (DSFB-CG) [9], [10]

Since adequate descriptions of SGFB-CG and DSFB-CS methods are given in [4] and [7], [8] respectively, this paper will focus on the design methodology for the SGFB-CS,

Jacques C.Rudell Department of Electrical Engineering University of Washington Seattle, Washington 98195-2500 Email: jcrudell@uw.edu

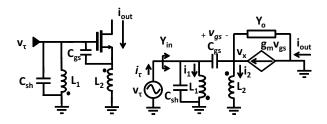

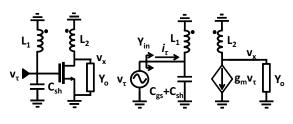

Fig. 1. Source Gate Feedback: Common Source Topology

DGFB and DSFB-CG TBFAs. Although several TBFAs have been reported in the recent literature, little insight is provided in the design and tradeoffs which are inherently associated with each approach. This is due, in part, to expressions for impedance matching which lend little intuition when optimizing the design. This paper provides a generic and systematic approach to the design of TBFAs. For each circuit the input admittance, modeled as a function of the transformer and transistor parameters, will be derived. This analytical model will be used to assess the impact of circuit parameters on bandwidth and stability. The first stage of a 5GHz wireless front end interfaced to a 50-ohm off-chip antenna will be used as a benchmark.

An accurate estimate of the device capacitances  $(C_{gs}, C_{gd}, C_{db})$  was obtained from the transistor's rf-model provided by the foundry using the 2-port Y-Parameter technique discussed in [11]. The effect of the finite output conductance,  $g_o$ , and load capacitance,  $C_o$ , has also been included. In each model an *n*-turn transformer, where  $n^2 = \frac{L_1}{L_2}$ , is used for feedback. In order to highlight the key factors influencing the bandwidth while maintaining concise expressions, inductors  $L_1$ ,  $L_2$  have been assumed to be ideal in the following analysis.

The SGFB is discussed in Sec.II. The DGFB topology is presented in Sec.III followed by DSFB-CG in Sec.IV. The simulation results to verify the models are included in each section. The different topologies are compared in Sec.V and finally, Sec.VI summarizes this work.

# II. SOURCE GATE FEEDBACK

The SGFB-CS topology has been widely used in recent literature. Applications for this technique have been demonstrated in the 1.575GHz GPS band [1], 3.1 - 10.6GHz UWB Band [2] as well as 75 - 91GHz W-Band systems [3]. The SGFB-CG based circuit was first introduced in [4] to boost effective

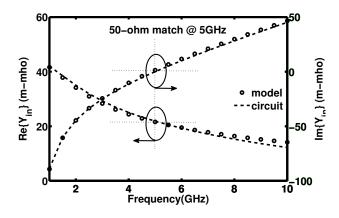

Fig. 2. Real and Imaginary Admittances: Model versus Circuit Simulations

trans-conductance  $(G_m)$  of a 5.8GHz LNA to minimize the noise figure while maintaining an impedance match.

## A. SGFB-CS Model

The small-signal model for the SGFB-CS circuit is shown Fig.1.The SGFB-CS TBFA has a dual feedback structure, with inductor  $L_2$  providing series-series feedback and a transformer comprised of the coupled inductors  $L_1$  and  $L_2$  providing series-shunt feedback. Using a conventional expression for the transformer while applying KCL and KVL,

$$\begin{pmatrix} v_{\tau} \\ v_{x} \end{pmatrix} = \begin{pmatrix} sn^{2}L_{2} & -k_{m}nsL_{2} \\ -k_{m}nsL_{2} & sL_{2} \end{pmatrix} \cdot \begin{pmatrix} i_{1} \\ i_{2} \end{pmatrix}$$

(1)

$$i_{\tau} = i_1 + sC_{gs}(v_{\tau} - v_x)$$

(2)

$$Y_o = g_o + sC_o \tag{3}$$

$$i_2 = (v_\tau - v_x)(g_m + sC_{gs})$$

(4)

From Eq.1-4 and defining  $\alpha = \frac{C_o}{C_{gs}}$  and  $L_{2l} = L_2(1 - k_m^2)$  it can be shown that

$$\frac{v_x}{v_\tau} = \frac{(g_m + sC_{gs})sL_{2l} - \frac{k_m}{n}}{1 + (g_o + g_m)sL_{2l} + s^2(C_o + C_{gs})L_{2l}}$$

(5)

$$\omega_r^2 (1+\alpha) C_{gs} L_{2l} = 1 \tag{6}$$

If the transformer is assumed to operate in resonance (Eq.6), then using Eq.5 an expression can be obtained for the input admittance,  $Y_{in}$ , at frequencies close to the carrier  $\omega_r$ . The impedance looking into the SGFB-CS stage is a parallel resonant network with a matched impedance at  $\omega_r$  given by Eq.7. This expression is valid for the practical condition,  $k \neq 1$ . When k = 1, the leakage inductance  $L_{2l} = 0$  and Eq.6 is no longer valid.

$$Re(Y_{in}) = \frac{\left(\frac{k_m}{n} + \frac{1}{1+\alpha}\right)^2}{(\omega_r L_{2l})^2 (g_o + g_m)}$$

(7)

The residual inductance at the input is resonated by adding a shunt capacitor  $C_{sh}$ , whose value is computed using Eq.8. The

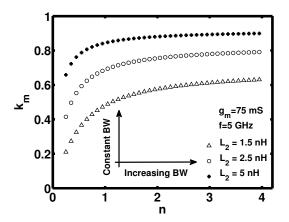

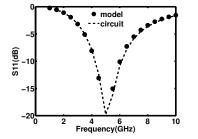

Fig. 3. Perfect Impedance Match Condition: Combinations of  $\{k_m, n\}$  required for 3 different values of  $L_2$

validity of Eq.7-8 are verified through circuit simulation results shown in Fig.2, where the  $\text{Re}\{Y_{in}\}$  and  $\text{Im}\{Y_{in}\}$  computed from the model are compared with the simulation results.

$$\omega_r(C_{gs} + C_{sh}) = \frac{1}{\omega_r L_{1l}} + \frac{g_m \sqrt{Re(Y_{in})}}{\sqrt{g_o + g_m}}$$

(8)

For a fixed device size and bias condition (constant  $g_m$  and  $g_o$ ), there are three design variables  $\{L_2, n, k_m\}$ . The relationship between the design variables and the design goal (Re( $Y_{in}$ )=20m-mho) given in Eq.7 can be re-formulated as Eq.9. All sets of  $\{L_2, n, k_m\}$  that satisfy Eq.9 result in a perfectly matched circuit. A sub-set of solutions (using a device with  $g_m = 75$ m-mho) are shown in Fig.3. In the figure  $k_m$  is plotted as a function of n ranging from  $\frac{1}{4}$  to 4 with three different values of  $L_2$ .

$$\beta k_m^2 + \frac{1}{n} k_m + (1 - \beta) = 0 \tag{9}$$

where,  $\beta = \omega_r L_2 \sqrt{Re(Y_{in})(g_o + g_m)}$

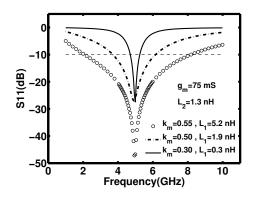

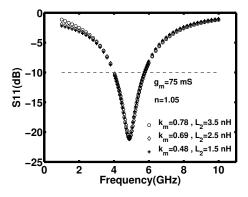

From Fig.3, it can be observed that as the value of n increases a higher  $k_m$  is required to maintain an  $|S_{11} < -10$ dB|. Fig.4 plots the  $S_{11}$  for different combinations of  $\{k_m, n\}$  with a constant  $L_2$ . As the value of  $k_m$  increases from 0.30 to 0.55, n needs to increase from 0.4 - 2, but this is associated with a 6x increase in the bandwidth. This highlights an interesting area vs. bandwidth trade-off in the SGFB-CS topology. This trend is shown in Fig.3, where increasing value of n on a constant  $L_2$  curve results in higher bandwidth.

For area constrained designs, Fig.5 plots  $S_{11}$  for different  $\{k_m, L_2\}$  for a fixed n. The closely matched plots indicate that as  $L_2$  is reduced for a fixed n, the bandwidth can be maintained by reducing the coupling between the transformer windings. This trend is shown in Fig.3, where increasing the value of  $L_2$  with a fixed n, yields a constant bandwidth.

# **III. DRAIN-GATE FEEDBACK**

The DGFB topology was first introduced in [6] as a technique to neutralize the gate-drain overlap capacitance,  $C_{qd}$ ,

Fig. 4. Variable Bandwidth Condition: Constant  $(g_m, L_2)$  while  $(k_m, n)$  are varied to maintain an input match

Fig. 5. Fixed Bandwidth Condition: Constant  $(g_m, n)$  while  $(k_m, L_2)$  are varied to maintain an input match

thus improving the stability of the amplifier. From Fig.6, expressions can be derived for the input admittance (Eq.10) and voltage gain (Eq.11) of the circuit.

$$\frac{i_{\tau}}{v_{\tau}} = s(C_{gs} + C_{sh}) + \frac{Y_o n^2 + g_m n k_m + \frac{1}{sL_1}}{1 + sL_2 Y_o (1 - k_m^2)}$$

(10)

$$\frac{v_x}{v_\tau} = \frac{g_m s L_{2l} + \frac{k_m}{n}}{1 - g_o s L_{2l}} \tag{11}$$

$$\omega_r L_2 Y_o(1 - k_m^2) \ll 1 \tag{12}$$

If component values are selected to meet the condition in Eq.12-13 at  $\omega_r$ , then Eq.10 can be simplified to Eq.14.

$$\omega_r (C_{sh} + C_{gs} + \frac{C_o}{n^2}) = \frac{1}{\omega_r L_1}$$

(13)

$$Re(Y_{in}) = \left(\frac{g_o}{n^2} + g_m \frac{k_m}{n}\right) \tag{14}$$

While possible to achieve an  $|S_{11} < -10$ dB| over a wide bandwidth, the DGFB feedback topology has limited applications because of the difficulty in achieving, simultaneously, both a high voltage gain and a 50-ohm input match. Assuming,  $g_m$  is high ( $\gg 20mS$ ), Eq.14 indicates that n > 1 is desired

Fig. 6. Drain Gate Feedback Topology

for input matching, whereas to obtain a voltage gain, Eq.11 requires n < 1. In [6] an extra strip-line based inductor was used in conjunction with the DGFB to realize the input matching network.

# IV. DRAIN-SOURCE FEEDBACK

The final method under consideration is the DSFB topology. A shunt-series positive feedback DSFB-CG circuit was introduced in [9] for a high-linearity 4.15-4.4 GHz front end receiver. [10] combines the  $G_m$  boosting topology introduced in [4] with the DSFB-CG architecture in [9], to achieve a wideband (1-8GHz) low-noise amplifier using dual-feedback.

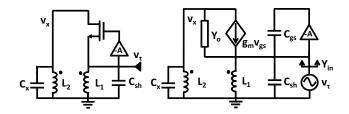

# A. DSFB-CG model

Since the transformer is used to provide positive feedback in this circuit, the stability condition has to be carefully analyzed. This requires careful selection of the output load capacitance,  $C_x$ , which has a significant impact on the stability of the DSFB-CG TBFA. The small-signal model for the DSFB-CG is shown in Fig.7. At  $\omega_r$  the admittance  $Y_{in}$  forms a parallel R-L-C circuit with the matched impedance given by Eq.15, where  $\alpha = A + 1$ . In order to obtain resonance at  $\omega_r$ ,  $C_{sh}$ is added to ensure Eq.16 is satisfied. The  $S_{11}$  measured from circuit simulation are compared with the results derived in Eq.15-16 in Fig.8.

$$Re(Y_{in}) = \alpha g_m \left(1 - \frac{\frac{k_m}{n}}{1 - \omega^2 C_x L_{2l}}\right) \tag{15}$$

$$\omega_r(\alpha C_{gs} + C_{sh}) = \frac{1}{\omega_r L_{1l}} \left(1 - \frac{k^2}{1 - \omega^2 C_x L_{2l}}\right)$$

(16)

The key merit of this topology is that it adds an additional degree of freedom in the trade-off between the power gain and input matching in the Common Gate (CG) amplifier [10]. The frequency dependent scaling factor introduced by the transformer allows  $g_m > \text{Re}(Y_{in})$  while still satisfying Eq.15. Assuming that  $C_{gd} \ll C_o$  and  $g_o \ll g_m \alpha$ , the voltage gain

of the circuit can be approximated by Eq.17,

$$\frac{v_x}{v_\tau} = \frac{s^2 C_o L_{2l} + sg_m \alpha L_{2l} - \frac{k_m}{n}}{s^2 (C_o + C_x) L_{2l} + sg_o L_{2l} + 1}$$

(17)

With a perfectly coupled transformer, the voltage gain of the circuit is  $\frac{1}{n}$ . Thus, in order to maximize the voltage gain the ratio  $\frac{L_2}{L_1}$  should be maximized while maintaining stability. To ensure the stability of any 2-port system, the fundamental criterion is to ensure that  $\operatorname{Re}(Y_{in}) > 0$  for all frequencies

Fig. 7. Drain-Source Feedback: Common Gate Topology

Fig. 8.  $S_{11}(dB)$ : Model versus circuit simulation

where the gain of the system is greater than unity. Based on Eq.15-17, the condition for stability can be expressed as

$$\frac{k_m}{n} < 1 - \omega^2 C_x L_2 (1 - k^2) \quad \forall \ \omega < \omega_x \ ; \ \frac{v_x}{v_\tau} (\omega_x) = 1 \ (18)$$

#### V. COMPARISON

Each TBFA has unique properties that motivate their application in a variety of circuits. Some of the important characteristics associated with each transformer-based feedback approach have been listed in Table.I. The DSFB-CG, SGFB-CG (voltage in-voltage out) and SGFB-CS (voltage in-current out) can be used to achieve a wideband input match. While the SGFB-CG and DSFB-CG are more area-efficient as voltage amplifiers, the SGFB-CS would be useful in a  $G_m$  stage of a wideband integrated mixer. As shown in Sec.II, the SGFB-CS could also be used for a narrow-band input match by controlling the magnetic coupling in the transformer.

While the CG stage is popular for wideband amplifiers, there is a lower bound on the achievable noise figure. The SGFB-CG can be used to break the noise figure-input match trade off. Similarly, the DSFB-CG TFBA is used to tackle the power gain-input match trade off in a CG stage. The DSFB-CG though, is only conditionally stable due to its positive feedback architecture. The stability criteria has been derived in Sec.IV.

The DGFB and DSFB-CS can be applied to neutralize the  $C_{gd}$  capacitance and thereby improve the reverse isolation,  $|S_{12}|$ , of the circuit. This is particularly important in low-voltage CMOS circuits where headroom limitations prevent an isolating cascode device from being used. Unfortunately, in the DGFB TBFA, 50-ohm impedance match and high voltage gain cannot be achieved simultaneously as shown in Sec.III. As a result additional inductors have to be used in conjunction with the DGFB resulting in an area penalty.

TABLE I TBFA PROPERTIES

|                       | SGFB-CS                                  | DGFB                              | DSFB-CG                           |

|-----------------------|------------------------------------------|-----------------------------------|-----------------------------------|

| Feedback              | Negative                                 | Negative                          | Positive                          |

| Function              | Trans-<br>conductance                    | Voltage-buffer                    | Voltage-gain                      |

| $\mathbf{Re}(Y_{in})$ | Eq.7                                     | Eq.14                             | Eq.15                             |

| Application           | Narrow-band/<br>Wide-band<br>Input match | device $C_{gd}$<br>Neutralization | Gain-Input<br>Match Trade-<br>off |

# VI. CONCLUSION

In this paper design techniques for SGFB-CS, DGFB and DSFB-CG TBFAs have been developed. For each of these structures, a complete frequency dependent input impedance model has been presented. The conditions to achieve narrowband or wideband input matching using a dual feedback SGFB-CS transconductance stage are derived. Results from SpectreRF simulations verify the validity of the derived results.

#### ACKNOWLEDGMENT

The authors would like to thank M.Boers and D.J.Allstot for valuable discussions on this topic.

#### REFERENCES

- A. C. Heiberg et.al., "A 250mV, 352µW GPS Receiver RF Front-End in 130nm CMOS", in *IEEE J.Solid State Circuits*, Vol.46, No.4, Pg.938-949, April 2011.

- [2] M. T. Reiha et.al., "A 1.2V Reactive-Feedback 3.1-10.6 GHz Low-Noise Amplifier in 0.13um CMOS", in *IEEE J.Solid State Circuits*, Vol.42, No.5, Pg.1023-1033, May 2007.

- [3] M. Khanpour et.al., "A Wideband W-Band Receiver Front-End in 65nm CMOS", in *IEEE J.Solid State Circuits*, Vol.43, No.8, Pg.1717-1730, August 2008.

- [4] X. Li et.al., "Gm-Boosted Common-Gate LNA and Differential Colpitts VCO/QVCO in 0.18-µm CMOS", in *IEEE J.Solid State Circuits*, Vol.40, No.12, Pg.2609-2619, December 2005.

- [5] C. Fu et.al., "Low-Noise Amplifier Design with Dual Reactive Feedback and Broadband Simultaneous Noise and Impedance Matching", in *IEEE Trans. on MTT*, Vol.58, No.4, Pg.795-806, April 2010.

- [6] M. P. V Heijden et.al. "On the design of unilaterial dual-loop feedback low noise amplifiers with simulation noise, impedance and IIP3 match", in *IEEE J.Solid State Circuits*, Vol.39, No.10, Pg.1727-1736, October 2004.

- [7] D. J. Cassan et.al., "A 1-V Transformer-Feedback Low-Noise Amplifier for 5-GHz Wireless LNA in 0.18-um CMOS", in *IEEE J.Solid State Circuits*, Vol.38, No.3, Pg.427-435, March 2003.

- [8] D. Gangopadhyay et.al., "A 1.6mW 5.4GHz transformer-feedback gmboosted current-reuse LNA in 0.18um CMOS", in *IEEE Proc. of ISCAS* 2010.

- [9] A. Liscidini et.al., "Common Gate Transformer Feedback LNA in a High IIP3 Current Mode RF CMOS Front-End", in *IEEE Proc. of CICC 2006*.

- [10] R. Ye et.al., "Wideband Common-Gate Low-Noise Amplifier with Dual-Feedback for Simultaneous Input and Noise Matching", in *IEEE Proc.* of *RFIC 2011*.

- [11] C. Enz et.al., "MOS Transistor Modeling for RF IC Design" in *IEEE J.Solid State Circuits* Vol.35, No.2, Pg.186-201, February 2000.